Correction exercices microprocesseur : Série 01

Exercices microprocesseur : Série 01

-

Exercice 01

-

Énoncé

- Vous pouvez visualiser l’énoncé de l’exercice

-

Solution

- Associez chaque mot de la liste suivante avec une des définitions proposées.

-

Exercice 02

-

Énoncé

- Vous pouvez visualiser l’énoncé de l’exercice

-

Solution

- Les Pentium dual core sont des core 2 duo « au rabais », de manière a avoir des processeurs entrée de gamme pour Intel.

- Les Pentium Dual Core ont un bus a 800 Mhz (au lieu de 1000), un cache L2 de 1Mo (au lieu de 2Mo) et fonctionnent a des fréquences + basses que les Core 2 Duo (de 1.6 a 2 Ghz, au lieu de 2Ghz a 3 Ghz).

- Le + puissant Pentium Dual Core (E2180) est inférieur au + petit Core 2 Duo (E4400)

- On n’additionne pas les fréquences des cores, ca n’a aucun sens, un Core 2 Duo a 2 Ghz signifie que les 2 cores sont a 2Ghz, ce n’est pas équivalent a un core a 4Ghz.

- L1 (niveau 1) cache – cache L1 stocke des informations pour une utilisation par le processeur. L1 cache L1 est très rapide mais aussi très coûteux. La plupart des processeurs ont un cache L1 divisés dans l’espace pour les données et l’espace pour les instructions.

- L2 (niveau 2) cache – cache L2 est la prochaine étape vers le bas de cache L1. . La plupart des processeurs d’aujourd’hui ont de cache L2, ce qui augmente lesperformances du cache. . La plupart des processeurs de bureau ont un cache L2 de 256 Ko environ, mais certains processeurs haut de gamme peuvent avoir autant que 2Mo.

- Un processeur « Dual Core » est un processeur du constructeur Intel contenant deux unités de calcul travaillant en parallèle.

- Chaque unité de calcul disposant de sa mémoire dédiée, elle peut travailler sur un processus différent de l’autre.

- Un Core 2 Duo est une évolution de l’architecture interne de ces processeurs, dans leur version ‘2 unités de calcul’.

- Le ‘Quad Core’ est une version ‘4 unités de calcul’ du Core 2, mais il s’agit en fait d’une version ‘2+2’, car deux processeurs ‘Core 2 Duo’ sont placés côte à côte sur le die (surface du processeur).

- Les Core i3, i5 et i7 sont les trois dernières gammes de processeurs d’Intel (sorties respectives en 2010, 2010 et 2008). Elles inaugurent une nouvelle architecture interne, et ses déclinaisons, ainsi que leur sockets (supports) correspondants, les sockets 1156, 1366, 1155 et 2011.

- Dotés de 2 à 6 unitées de calcul, ces processeur supplantent les précédents processeurs d’Intel (des séries Core, Core 2) par leurs performances.

- Certains sont aussi doté d’un coprocesseur graphique, l’IGP (pour Integrated Graphic Processor), permettant de se passer de carte graphique, qu’elle soit ajoutée sur la carte-mère, ou intégrée à cette dernière.

- L’Intel Core i3 correspond à l’entrée de gamme des processeurs Intel Core, tandis que l’Intel Core i5 constitue le milieu de gamme, derrière l’Intel Core i7 et l’Intel Core i9, de gammes supérieures. Chaque gamme est composée de différentes versions de processeurs offrant des performances variées.

- En effet, depuis l’Intel Core, ce ne sont pas seulement le nombre de cœurs, la mémoire cache et la fréquence qui déterminent la performance d’un CPU. Les technologies embarquées (Hyper-Threading, Turbo Boost) dans ces processeurs influent également sur leur puissance.

-

Exercice 03

-

Énoncé

- Vous pouvez visualiser l’énoncé de l’exercice

-

Solution

- Les registres sont les éléments de mémoire les plus rapides. Ils sont situés au niveau du processeur et servent au stockage des opérandes et des résultats intermédiaires

- Le registre d’état est généralement composé de 8 bits à considérer individuellement. Chacun de ces bits est un indicateur dont l’état dépend du résultat de la dernière opération effectuée par l’UAL.

- On les appelle indicateur d’état ou flagou drapeaux. Dans un programme le résultat du test de leur état conditionne souvent le déroulement de la suite du programme. On peut citer par exemple les indicateurs de :

- retenue (carry : C

- retenue intermédiaire (Auxiliary-Carry : AC)

- signe (Sign : S)

- débordement (overflow : OV ou V)

- zéro (Z)

- parité (Parity : P)

- La taille de l’espace mémoire maximum=216 8 bits =24 210octets= 16 KO.

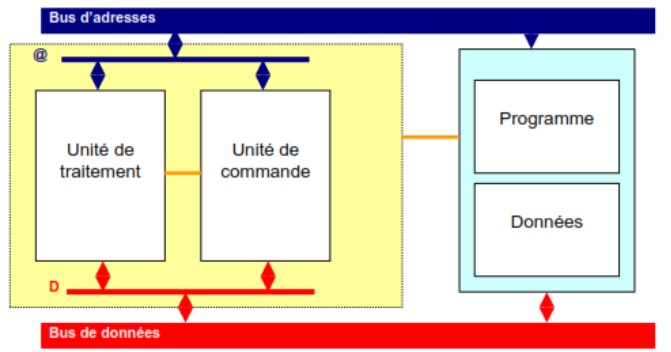

- Un microprocesseur est construit autour de deux éléments principaux :

-

Une unité de commande

- :Elle permet de séquencer le déroulement des instructions.

- Elle effectue la recherche en mémoire de l’instruction.

- Comme chaque instruction est codée sous forme binaire, elle en assure le décodage pour enfin réaliser son exécution puis effectue la préparation de l’instruction suivante.

-

Une unité de traitement

- Une unité de traitement: C’est le cœur du microprocesseur. Elle regroupe les circuits qui assurent les traitements nécessaires à l’exécution des instructions.

-

L’unité de commande

- L’unité de commande et l’unité de traitement sont associées à des registres chargées de stocker les différentes informations à traiter. Ces trois éléments sont reliés entre eux par des bus interne permettant les échanges d’informations.

- l’énoncé de l’exercice

| Mots | Définitions |

|---|---|

| a- Port série | 16. Dispositif d’E/S du micro-ordinateur accessible par un programme dans lequel les données sont transmises bit après bit de manière asynchrone. Il peut connecter le modem au micro-ordinateur. |

| b- Mémoire morte | 20. Mémoire interne dont le contenu peut être lu mais non modifié. |

| c- Horloge | 11. Cristal de quartz vibrant à une fréquence déterminée, produisant des signaux périodiques qui servent à synchroniser les tâches d’un microprocesseur. |

| d- Transistor | 21. Sorte de commutateur électronique servant à contrôler le passage du courant électrique. Sert à établir les niveaux de courant correspondant aux deux états numériques 0 et 1. |

| e- Bit | 8. Unité d’information |

| f- CPU | 17. Unité principale de traitement d’un ordinateur, généralement contenue dans un circuit intégré unique. |

| g- Puce | 5. Ensemble de circuits gravés sur une plaque de silicium. |

| h- Cache | 3. Circuit spécialisé comportant une petite quantité de mémoire ultra rapide pour rendre les informations fréquemment demandées immédiatement accessibles au processeur. |

| i- le séquenceur | 25. définit le nombre de cases mémoire accessibles ; |

| j- Chiffre hexadécimal | 7. Chiffre en base 16 |

| k- Bus | 18. Ensemble des lignes transportant les signaux qui permettent au microprocesseur de communiquer avec ses mémoires internes et ses périphériques. |

| l- Unité Arithmétique et Logique | 22. Partie du microprocesseur qui exécutent les calculs arithmétique (addition, soustraction, …) et les opérations logiques (et, ou, …). |

| m- Circuit intégré | 4. Circuit intégré couramment utilisé pour construire la mémoire centrale. |

| n-Le bus d’adresse | 24. c’est la partie qui permet de synchroniser les différents éléments du processeur. En particulier, il initialise les registres lors du démarrage de la machine et il gère les interruptions ; |

| o- RAM | 13. Mémoire rapide à accès direct, Random Access Memory. |

| p- ROM | 23. Mémoire morte |

| q- Système d’exploitation | 12. Programme nécessaire à la gestion des ressources en matériel et logiciel d’un ordinateur. |

| r- Unité de Contrôle | 6. Composante du microprocesseur qui indique quoi faire au bus, à la mémoire, aux dispositifs d’E/S en fonction des instructions du programme exécuté. |

| s- Clavier | 1. Dispositifs d’entrée de données |

| t- Carte Mère | 15. Principale carte de circuits imprimés dans un ordinateur. |

| u- Imprimante | 2. Périphérique de sortie |

| v- Pascal | 10. Langage de programmation |

| w- Port parallèle | 14. Dispositif d’E/S du micro-ordinateur accessible par un programme qui transporte simultanément les 8 bits d’un mot au travers d’un ensemble de conducteurs. Il peut connecter l’imprimante au micro-ordinateur. |

| x-Le bus de commande | 9. définit la gestion du processeur IRQ, RESET etc. |

| y- Registre | 19. Petite mémoire contenue dans le microprocesseur destiné à stocker de manière très temporaire un certain nombre d’informations comme les résultats intermédiaires d’un calcul ou l’adresse de la prochaine instruction à exécuter . 25. définit le nombre de cases mémoire accessibles ; |

- l’énoncé de l’exercice

-

Question:01

Question:02

Question:05

Question:05

- l’énoncé de l’exercice

-

Question:01

Question:02

Question:03

Question:04